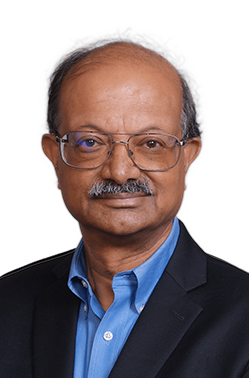

Jamal Deen

Professor at McMaster University

Bio.: Distinguished University Professor; Senior Canada Research Chair in Information Technology; Director, Micro- and Nano-Systems Laboratory (MNSL); President, Academy of Science, Royal Society of Canada (2015-17); FRSC Fellow, Royal Society of Canada; A-CAS Academician (Foreign Member), Chinese Academy of Sciences; FCAE Fellow, Canadian Academy Engineering; FNASI Fellow (Foreign), National Academy of Sciences, India; FINAE Fellow (Foreign), Indian National Academy Engineering; MEASA Member, European Academy of Sciences and Arts; FTWAS Fellow, The World Academy of Sciences; FIEEE Fellow, Institute of Electrical & Electronics Engineers; FAPS Fellow, American Physical Society; FECS Fellow, Electrochemical Society; FAAAS Fellow, American Association for the Advancement of Science; FEIC Fellow, Engineering Institute of Canada.

In the couple of few decades, the field of flexible organic/polymeric electronics has advanced significantly. This has been primarily because of the developments of new materials, improvements in the quality organic/polymeric materials, as well as the processing techniques, technologies and device designs. For example, roll-to-roll, sheet-to-sheet or printing technologies are being proposed as suitable manufacturing candidates because they can be carried out at room temperature, do not require the kind of clean room environment needed for traditional semiconductor manufacturing, and are very suitable for very low-cost, high volume production. Further, these advances are mostly stimulated by the promise of lighter and more robust devices and systems for applications that include large-area electronics, active matrix large-area displays, large-area solar cells, interactive displays, and conformable sensors and actuators. However, despite these advances, there remain challenges in the large-scale transfer of research prototypes into manufactured products. Furthermore, a major the limitation is the lack of accurate and computationally efficient compact models for organic/polymeric thin film transistors with associated parameter extraction techniques. In this presentation, we will discuss recent compact models and illustrate the merits and limitations of several of them as part of the electronic design automation platform. In this presentation, we will discuss our progress in developing industry-viable static and dynamic compact models for flexible transistors with predictable performance and the associated parameter extraction schemes including evolutionary computation for parameter extraction. Finally, we will present several on-going modeling challenges including illumination, hysteresis and contacts effects, as well as models that can predict stability, reliability, and lifetime.